Timing diagram of 2:1 mux using cmos logic in dsch2 Figure 3 from power optimization of 8:1 mux using transmission gate Mux 16 two construct multiplexer diagram block line multiplexers constructed dec2005 suitable assumptions 5m makes any if

8X1 Mux Logic Diagram : Using 8 1 Multiplexers To Implement Logical

Modern circuit design — cosc2325 fall2018 documentation Multiplexer ic logic combinational circuits table truth tutorial electronics below figure Verilog code for 8:1 multiplexer (mux)

Latch mux timing flop programmable triggered synthesis cycle edge clk

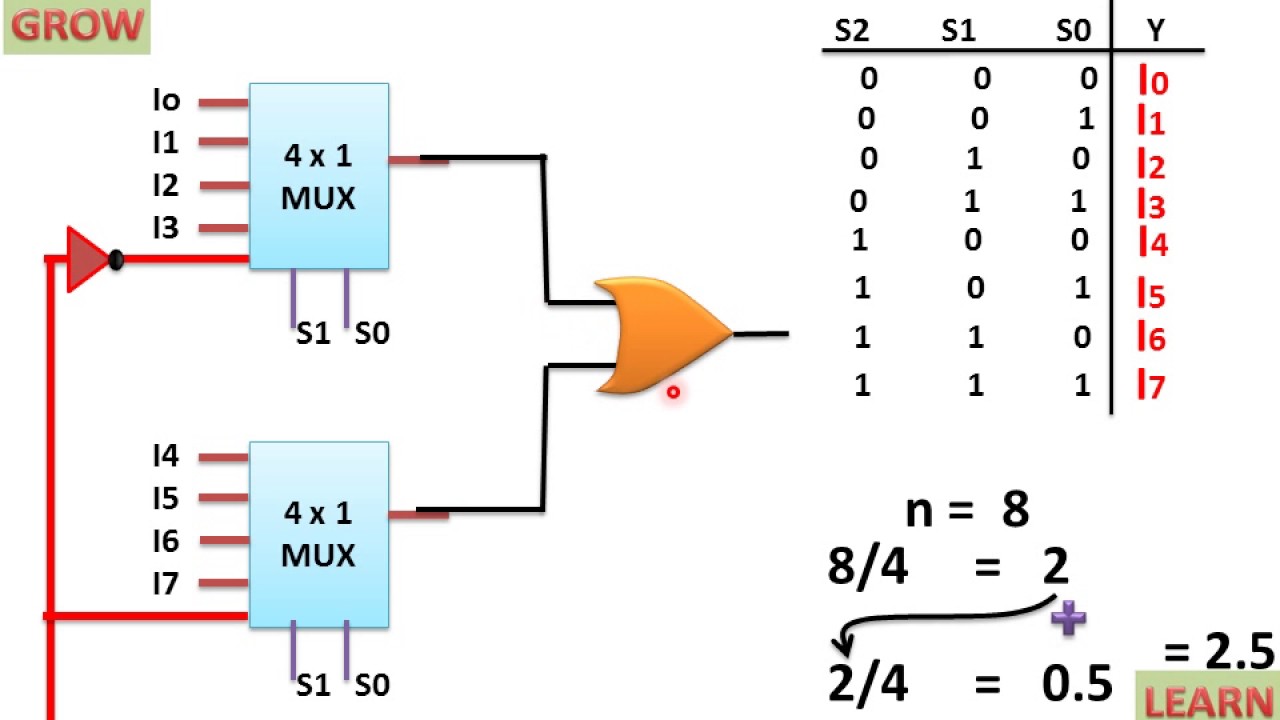

Multiplexer logic mux 4x1 demultiplexer vhdl multiplexers verilog block implement cheggConstruct 16-to-1 line multiplexer with two 8-to-1 line multiplexers Cmos mux timing logicMultiplexer mux nand inputs multiplexing boolean expression dip fortunately elcho.

8x1 mux multiplexer 4x1 logic implementation implement multiplexers logical 2x1Mux tgl logic optimization gating (pdf) dual-edge-triggered flip-flop-based high-level synthesis withMultiplexer mux implement plc truth logic sanfoundry gates.

8x1 mux logic diagram : using 8 1 multiplexers to implement logical

Plc program to implement 8:1 multiplexerMultiplexer mux verilog logic 8x1 multiplexers implemented simplicity 4x1 mux logic diagram / solved: write vhdl programs for a 4x1.

.

(PDF) Dual-Edge-Triggered Flip-Flop-Based High-Level Synthesis with

Construct 16-to-1 line multiplexer with two 8-to-1 line multiplexers

Modern Circuit Design — COSC2325 fall2018 documentation

4X1 Mux Logic Diagram / Solved: Write VHDL Programs For A 4x1

Timing Diagram of 2:1 MUX using CMOS Logic in DSCH2 | Download

PLC Program to Implement 8:1 Multiplexer - Sanfoundry

8X1 Mux Logic Diagram : Using 8 1 Multiplexers To Implement Logical

Verilog code for 8:1 Multiplexer (MUX) - All modeling styles